Xilinx CPLD:

XC9572 CPLD Board

- all pins are available on headers

- JTAG header for progamming

- onboard 2,5V and 3.3 V power supply

- IO reference voltage selection

- socket for crystal oscillator

XC9572 CPLD features:

- 5 ns pin-to-pin logic delays

- System frequency up to 178 MHz

- 72 macrocells with 1,600 usable gates

- Optimized for high-performance 3.3V systems

- Low power operation

- 5V tolerant I/O pins accept 5V, 3.3V, and 2.5V signals

- 3.3V or 2.5V output capability

Advanced 0.35 micron feature size CMOS Fast FLASH™ technology - Advanced system features

- In-system programmable

- Superior pin-locking and routability with Fast CONNECT™ II switch matrix

- Extra wide 54-input Function Blocks

- Up to 90 product-terms per macrocell with individual product-term allocation

- Local clock inversion with three global and one product-term clocks

- Individual output enable per output pin

- Input hysteresis on all user and boundary-scan pin inputs

- Bus-hold circuitry on all user pin inputs

- Full IEEE Standard 1149.1 boundary-scan (JTAG) - Excellent quality and reliability

- Endurance exceeding 10,000 program/erase cycles

- 20 year data retention

- ESD protection exceeding 2,000V - Fast concurrent programming

- Slew rate control on individual outputs

- Pin-compatible with 5V-core XC9572 device

Xilinx FPGA:

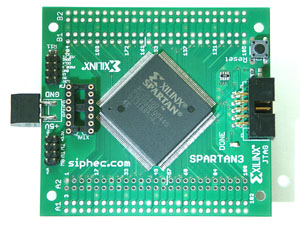

XC3S400 TinyBoard

- Xilinx FPGA XC3S400PQ208

- JTAG header, ModePin header, Config header

- crystal sockel

- reset push button, done led

- 3.5 to 5.5 Volt input connector

Bottom side:

- 3.3 Volt regulator for Config Flash and external use

- 2.5 Volt regulator for Auxiliary

- 1.2 Volt regulator for core voltage

- a couple of bypass capacitators

- configuration flash XCF02S

- all pins are available on headers (2.54mm-/0.1" pitch)

- all pins can be used, max. 144 User I/Os, max. 62 Differential Pairs, 8 GCLKs, 22 VREFs

- available with an without soldered 2.54mm pin headers

- version with XC2S200 possible

- DDR-DIMM Board supports up to 2 GB DDR SDRAM

Xilinx JTAG:

Xilinx JTAG (programmer)